# Micro Processor & Controller

# TMS320F28335 – Concerto Data Manual

### **Features**

#### 1.1 Features

- High-Performance Static CMOS Technology

- Up to 150 MHz (6.67-ns Cycle Time)

- 1.9-V/1.8-V Core, 3.3-V I/O Design

- High-Performance 32-Bit CPU (TM\$320C28x)

- IEEE-754 Single-Precision Floating-Point Unit (FPU) (F2833x only)

- 16 x 16 and 32 x 32 MAC Operations

- 16 x 16 Dual MAC

- Harvard Bus Architecture

- Fast Interrupt Response and Processing

- Unified Memory Programming Model

- Code-Efficient (in C/C++ and Assembly)

- Six Channel DMA Controller (for ADC, McBSP, ePWM, XINTF, and SARAM)

- 16-bit or 32-bit External Interface (XINTF)

- Over 2M x 16 Address Reach

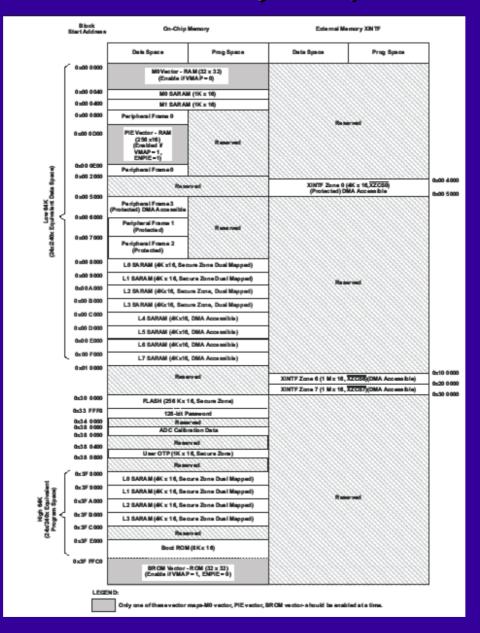

- On-Chip Memory

- F28335/F28235: 256K x 16 Flash, 34K x 16 SARAM

- F28334/F28234: 128K x 16 Flash, 34K x 16 SARAM

- F28332/F28232: 64K x 16 Flash, 26K x 16 SARAM

- 1K x 16 OTP ROM

- Boot ROM (8K x 16)

- With Software Boot Modes (via SCI, SPI, CAN, I2C, McBSP, XINTF, and Parallel I/O)

- Standard Math Tables

- Clock and System Control

- Dynamic PLL Ratio Changes Supported

- On-Chip Oscillator

- Watchdog Timer Module

- GPI00 to GPI063 Pins Can Be Connected to One of the Eight External Core Interrupts

- Peripheral Interrupt Expansion (PIE) Block That Supports All 58 Peripheral Interrupts

- 128-Bit Security Key/Lock

- Protects Flash/OTP/RAM Blocks

- Prevents Firmware Reverse Engineering

- Enhanced Control Peripherals

- Up to 18 PWM Outputs

- Up to 6 HRPWM Outputs With 150 ps MEP Resolution

- Up to 6 Event Capture Inputs

- Up to 2 Quadrature Encoder Interfaces

- Up to 8 32-bit/Nine 16-bit Timers

- Three 32-Bit CPU Timers

- Serial Port Peripherals

- Up to 2 CAN Modules

- Up to 3 SCI (UART) Modules

- Up to 2 McBSP Modules (Configurable as SPI)

- One SPI Module

- One Inter-Integrated-Circuit (I2C) Bus

- 12-Bit ADC, 16 Channels

- 80-ns Conversion Rate

- 2 x 8 Channel Input Multiplexer

- Two Sample-and-Hold

- Single/Simultaneous Conversions

- Internal or External Reference

- Up to 88 Individually Programmable,

Multiplexed GPIO Pins With Input Filtering

- JTAG Boundary Scan Support (f)

- Advanced Emulation Features

- Analysis and Breakpoint Functions

- Real-Time Debug via Hardware

- Development Support Includes

- ANSI C/C++ Compiler/Assembler/Linker

- Code Composer Studio™ IDE

- DSP/BIOS™

- Digital Motor Control and Digital Power Software Libraries

- Low-Power Modes and Power Savings

- IDLE, STANDBY, HALT Modes Supported

- Disable Individual Peripheral Clocks

- Package Options

- Lead-free Green Packaging

- Thin Quad Flatpack (PGF)

- MicroStar BGA™ (ZHH)

- Plastic BGA (ZJZ)

- Temperature Options:

- A: -40°C to 85°C (PGF, ZHH, ZJZ)

- S: -40°C to 125°C (ZJZ)

- Q: –40°C to 125°C (ZJZ)

- IEEE Standard 1149.1-1990 Standard Test Access Port and Boundary Scan Architecture

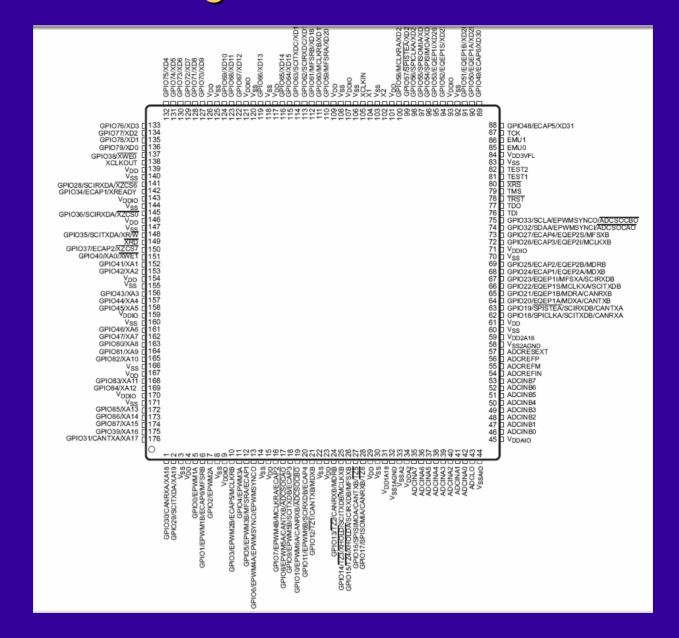

### Pin Assignment – 176 LQFP

### Pin Descriptions

### Click

TMS320F28335/28334/28332 TMS320F28235/28234/28232 Digital Signal Controllers (DSCs) 8PR8439E-JUNE 2007-REVISED SEPTEMBER 2008

www.tl.com

#### 2.2 Signal Descriptions

Table 2-3 describes the signals. The GPIO function (shown in Italics) is the default at reset. The peripheral signals that are listed under them are alternate functions. Some peripheral functions may not be available in all devices. See Table 2-1 for details. Inputs are not 5-V tolerant. All pins capable of producing an XINTF output function have a drive strength of 8 mA (typical). This is true even if the pin is not configured for XINTF functionality. All other pins have a drive strength of 4-mA drive typical (unless otherwise indicated). All GPIO pins are IVO/Z and have an internal pullup, which can be selectively enabled/disabled on a per-pin basis. This feature only applies to the GPIO pins. The pullups on GPIO0-GPIO11 pins are not enabled at reset. The pullups on GPIO12-GPIO34 are enabled upon reset.

Table 2-3. Signal Descriptions

| NAME                |              | PIN NO       | L            | DESCRIPTION (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|--------------|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | PGF<br>PIN # | ZHH<br>BALL# | ZJZ<br>BALL# |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| JTAG                |              |              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TRST                | 78           | M10          | L11          | JTAG lest reset with internal pulldown. TRST, when driven high, gives the scan system control of the operations of the device. If this signal is not connected or driven low, the device operates in its functional mode, and the lest reset signals are ignored. NOTE: TRST is an active high test pir and must be maintained low at all times during normal device operation. An external pulldown resistor is recommended on this pin. The value of this resistor should be based on drive strength of the debugger pods applicable to the design. A 2.2-xth resistor generally offers adequate protection. Since this application-specific, it is recommended that each target board be validated for proper operation of the debugger and the application. (i. 1)                                         |

| TCK                 | 87           | N12          | M14          | JTAG test clock with Internal pullup (I, ↑)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TMS                 | 79           | P10          | M12          | JTAG test-mode select (TMS) with Internal pullup. This serial control input is clocked into<br>the TAP controller on the rising edge of TCK. (I, T)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TDI                 | 76           | М9           | N12          | JTAG test data input (TDI) with internal pullup. TDI is clocked into the selected register<br>(Instruction or data) on a rising edge of TCK. (I, 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TDO                 | 77           | К9           | N13          | JTAG scan out, test data output (TDO). The contents of the selected register (instruction or data) are shifted out of TDO on the failing edge of TCK. (O/Z 8 mA drive)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EMUO                | 85           | L11          | N7           | Emulator pin D. When TRST is driven high, this pin is used as an interrupt to or from the emulator system and is defined as inpulifought through the JTAG scan. This pin is also used to put the device into boundary-scan mode. With the EMUD pin at a logic-high state and the EMUT pin at a logic-how state, a risingle edge on the TRST pin would latch the device into boundary-scan mode. (IVOZ, 8 mA drive T). NOTE: An external pullup resistor is recommended on this pin. The value of this resistor should be based on the drive strength of the debugger pods applicable to the design. A 2.2-AUD to 4.7-AU resistor is generally adequate. Since this is application-specific, it is recommended that each target board be validated for proper operation of the debugger and the application.    |

| EMU1                | 86           | P12          | P8           | Emulator pin 1. When TRST is driven high, this pin is used as an interrupt to or from the emulator system and is defined as inputouptub through the JTAGs can. This pin is also used to put the device into boundary-scan mode. With the EMU0 pin at a logic-high state and the EMU1 pin at a logic-how state, a rising edge on the TRST pin would latch the device into boundary-scan mode. (IVIO.2, 8 ml Ad rive 1). NOTE: An external pullup resistor is recommended on this pin. The value of this resistor should be based on the drive strength of the debugger post application to the design. A 2.2-XLD of 4.7-XLD resistor is generally adequate. Since this is application-specific, if is recommended that each target board be validated for proper operation of the debugger and the application. |

| FLASH               |              |              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>DDSWFL</sub> | 84           | M11          | L9           | 3.3-V Flash Core Power Pin. This pin should be connected to 3.3 V at all times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TEST1               | 81           | K10          | M7           | Test Pin. Reserved for TI. Must be left unconnected. (I/O)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TEST2               | 82           | P11          | L7           | Test Pin. Reserved for TI. Must be left unconnected. (I/O)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

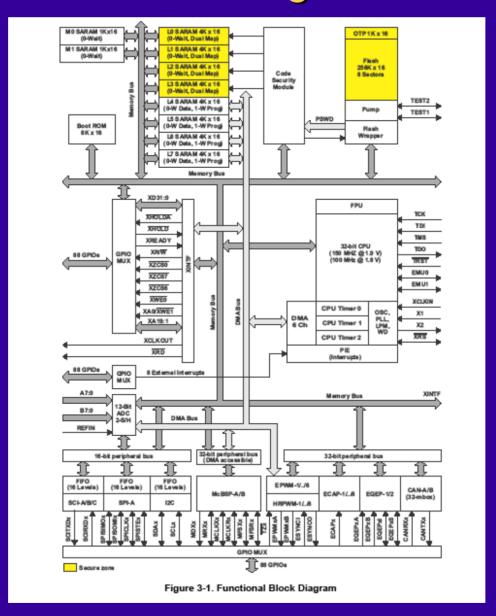

# **Block Diagram**

## **Memory Map**

### **CPU**

### 3.2.1 C28x CPU

The F2833x/F2823x (C28x+FPU) family is a member of the TMS320C2000™ digital signal controller (DSC) platform. The C28x+FPU based controllers have the same 32-bit fixed-point architecture as TI's existing C28x DSCs, but also include a single-precision (32-bit) IEEE 754 floating-point unit (FPU). It is a very efficient C/C++ engine, enabling users to develop their system control software in a high-level language. It also enables math algorithms to be developed using C/C++. The device is as efficient in DSP math tasks as it is in system control tasks that typically are handled by microcontroller devices. This efficiency removes the need for a second processor in many systems. The 32 x 32-bit MAC 64-bit processing capabilities enable the controller to handle higher numerical resolution problems efficiently. Add to this the fast interrupt response with automatic context save of critical registers, resulting in a device that is capable of servicing many asynchronous events with minimal latency. The device has an 8-level-deep protected pipeline with pipelined memory accesses. This pipelining enables it to execute at high speeds without resorting to expensive high-speed memories. Special branch-look-ahead hardware minimizes the latency for conditional discontinuities. Special store conditional operations further improve performance.

The F2823x family is also a member of the TMS320C2000™ digital signal controller (DSC) platform but it does not include a floating-point unit (FPU).

### **Memory Bus**

### 3.2.2 Memory Bus (Harvard Bus Architecture)

As with many DSC type devices, multiple busses are used to move data between the memories and peripherals and the CPU. The C28x memory bus architecture contains a program read bus, data read bus and data write bus. The program read bus consists of 22 address lines and 32 data lines. The data read and write busses consist of 32 address lines and 32 data lines each. The 32-bit-wide data busses enable single cycle 32-bit operations. The multiple bus architecture, commonly termed Harvard Bus, enables the C28x to fetch an instruction, read a data value and write a data value in a single cycle. All peripherals and memories attached to the memory bus will prioritize memory accesses. Generally, the priority of memory bus accesses can be summarized as follows:

Highest: Data Writes (Simultaneous data and program writes cannot occur on the memory bus.)

Program Writes (Simultaneous data and program writes cannot occur on the memory bus.)

Data Reads

Program Reads (Simultaneous program reads and fetches cannot occur on the memory bus.)

Lowest: Fetches (Simultaneous program reads and fetches cannot occur on the memory bus.)