# Component Declaration (notes)

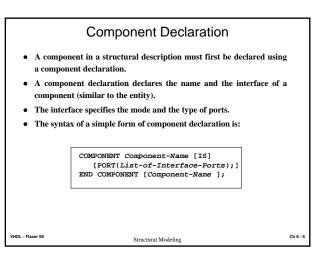

- The *component-name* may or may not refer to the name of an entity already existing in a library. If it does not, it must be explicitly bound to an entity.

- The binding information can be specified using a configuration.

- The List-Of-Interface-Ports specifies the name, mode, and type for each port of the component in a manner similar to that specified in an entity declaration.

- · The names of the ports may also be different from the names of the ports in the entity to which it may be bound (different port names can be mapped in a configuration). For while, we will assume that an entity of the same name as that of the component already exists and that the name, mode, and type of each port matches the corresponding ones in the component

- · Configurations are discussed in the next chapter.

VHDL - Flaxer Eli

Structural Modeling

Ch 8 - 7

Structural Modeling

Actuals and Formals • If a port in a component instantiation is not connected to any signal, the keyword OPEN can be used to signify that the port is not connected. · For example: PORT (d, clk: IN bit:='0'; q, qb: OUT bit); END COMPONENT; COMPONENT dff d1: dff PORT MAP (OPEN, ck, s1, OPEN); • The second input port of the dff component is not connected to any signal. An input port may be left open only if its declaration specifies an initial value. For the previous component instantiation statement to be legal, port d of the component declaration for dff must have an initial value expression. while the output port qb not. A port of any other mode may be left unconnected as long as it is not an unconstrained array. Structural Modeling

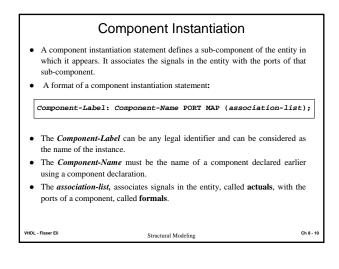

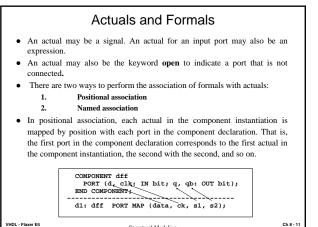

## Actuals and Formals

- In named association, an association-list is of the form:

formal<sub>1</sub> => actual<sub>p</sub> formal<sub>2</sub> => actual<sub>2</sub> ... formal<sub>n</sub> => actual<sub>n</sub>

- For example:

### COMPONENT dff PORT (d, clk: IN bit; q, qb: OUT bit); END COMPONENT;

dl: dff PORT MAP (clk => ck, d => data, qb => s2, q => s1);

- In named association, the ordering of the associations is not important since the mapping between the actuals and formals is explicitly specified.

- An important point to note is that the scope of the formals is restricted to be within the port map part of the instantiation for that component.

VHDL - Flaxer Eli

HDL - Flaxer Eli

Structural Modeling

# Actuals / Formals Type and Mode The types of the formal and actual being associated must be the same. The modes of the ports must conform to the rule that if the formal is readable, so must the actual be; and if the formal is writable, so must the actual be.

- Locally declared signal is considered to be both readable and writable, such a signal may be associated with a formal of any mode.

- If an actual is a port of mode in, it may not be associated with a formal of mode out or inout; if the actual is a port of mode out, it may not be associated with a formal of mode in or inout; if the actual is a port of mode inout, it may be associated with a formal of mode in, out, or inout.

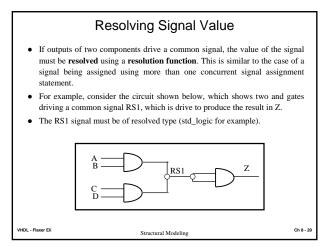

- It is important to note that an actual of mode **out** or **inout** indicates the presence of a source for that signal, and therefore, it must be resolved if that signal is multiply driven.

- A **buffer** port can never have more than one source; therefore, the only kind of actual that can be associated with a **buffer** port is another **buffer** port or a signal that has at most one source.

Structural Modeling

VHDL - Flaxer Eli

Ch 8 - 13

Ch 8 - 15

Ch 8 - 14

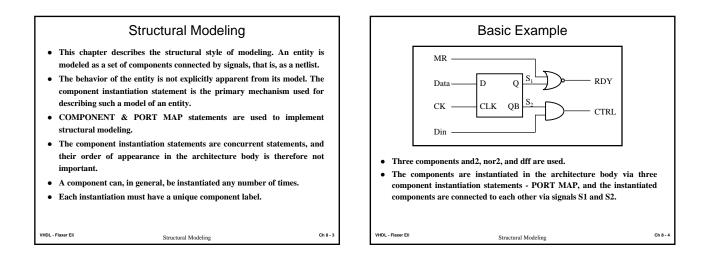

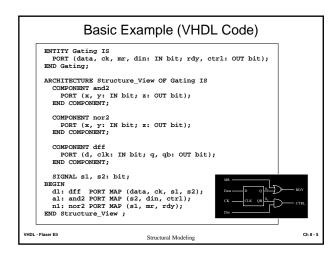

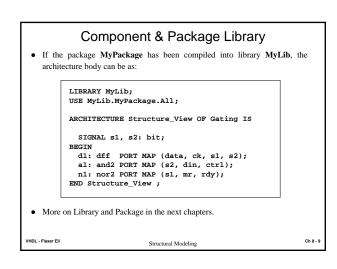

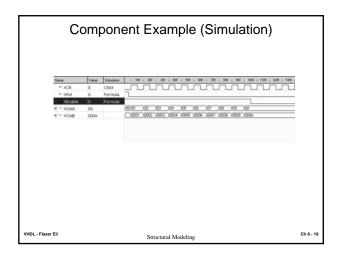

# Component Model Structural models can be simulated and synthesize only after the entities that the components represent are modeled and placed in a design library. The lowest-level entities must be behavioral models (or dataflow). Consider the components instantiation A1, N1, and D1 in the basic example. Assume that those instance is bound to an entity with the same name and identical port names. The library must include the model of those components. More on Library and Package in the next chapters.

Structural Modeling

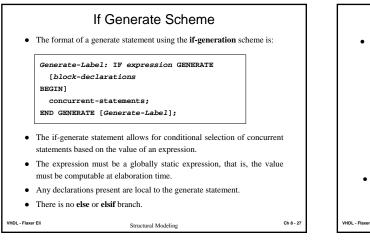

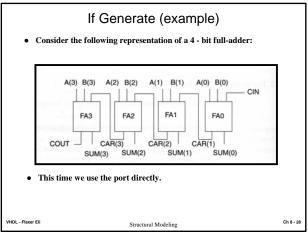

| If - Generate (example code)                                       |

|--------------------------------------------------------------------|

| ARCHITECTURE if_generate OF full_add4 IS<br>COMPONENT fa           |

| PORT (pa, pb, pc: IN bit; pcout, psum: OUT bit);<br>END COMPONENT; |

| <pre>SIGNAL car: bit_vector(3 DOWNTO 1);</pre>                     |

| BEGIN                                                              |

| gk: FOR k IN 3 DOWNTO 0 GENERATE                                   |

| ck0: IF k = 0 GENERATE                                             |

| <pre>f1: fa PORT MAP(cin,a(k),b(k),car(k+1),sum(k));</pre>         |

| END GENERATE ck0;                                                  |

| ck1: IF k > 0 AND k < 3 GENERATE                                   |

| <pre>f1: fa PORT MAP(car(k),a(k),b(k),car(k+1),sum(k));</pre>      |

| END GENERATE ck1;                                                  |

| ck3: IF k = 3 GENERATE                                             |

| <pre>f1: fa PORT MAP(car(k),a(k),b(k),cout,sum(k));</pre>          |

| END GENERATE ck3;                                                  |

| END GENERATE gk;                                                   |

| END if_generate;                                                   |

| - Flaxer Eli Structural Modeling Ch 8 - 29                         |